# MCA-20104 COMPUTER ORGANIZATION Instruction: 4 Periods/week Time: 3 Hours Credits: 4 Internal: 25 Marks External: 75 Marks Total: 100 Marks UNIT-I

### **Digital Logic Circuits:**

Digital Computers, Logic Gates, Boolean Algebra, Map Simplification, Combinational Circuit, Flip-flops Sequential Circuits.

### **Digital Components:**

Integrated Circuits, Decoders, Multiplexes, Registers, Shift Registers, Counters, Memory Unit.

### UNIT-II

### **Data Representation:**

Data Types, Complements, Fixed-point Representation, Floating point Representation.

### **Register Transfer and Micro Operations:**

Register Transfer Language, Register Transfer, Bus and Memory Transfer, Arithmetic Micro Operations, Assembly language Instructions, 8085 Microprocessor Instruction Set,8085 Architecture.

### **UNIT-III**

### **Basic Computer Organization and Design:**

Instruction Codes, Computer Register, Computer Instructions, Timing and Control, Instruction

Cycle, Memory Reference Instructions, Input-Output, Interrupt.

### **Central Processing Unit:**

Introduction, General Register Organization, Stack Organization, Instruction formats, addressing modes.

### **UNIT-IV**

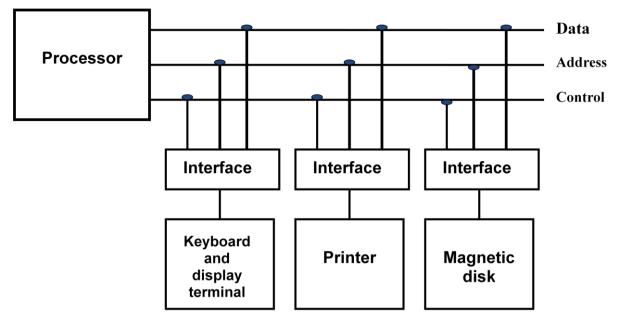

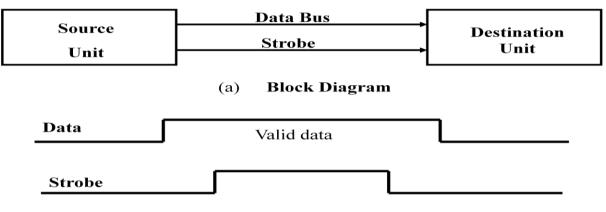

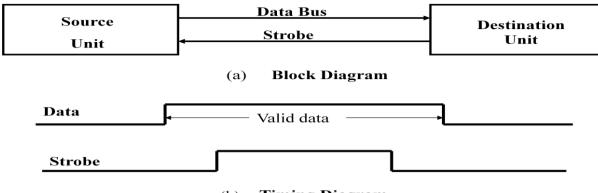

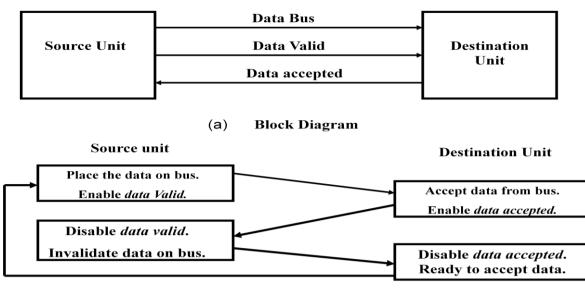

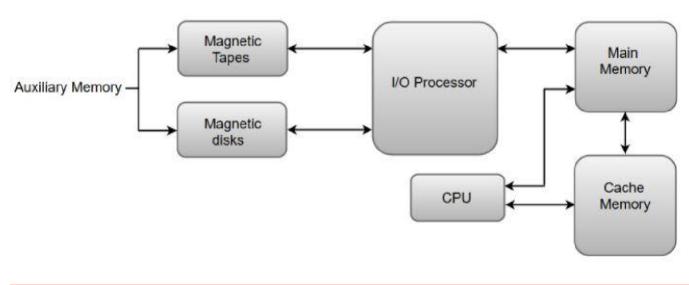

### **Input /Output Organization:**

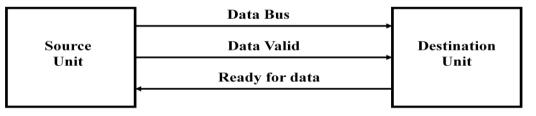

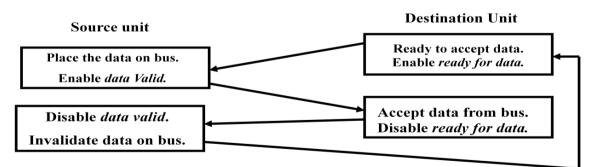

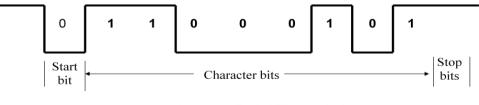

Peripherals Devices, I/O Interface, Asynchronous Data Transfer, Mode of Transfer, Priority Interrupt, Direct memory access, Input – Output Processor(IOP).

### **Memory Organization:**

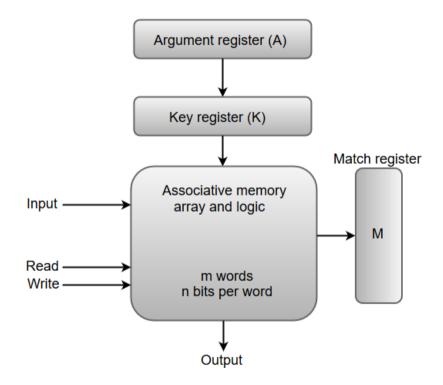

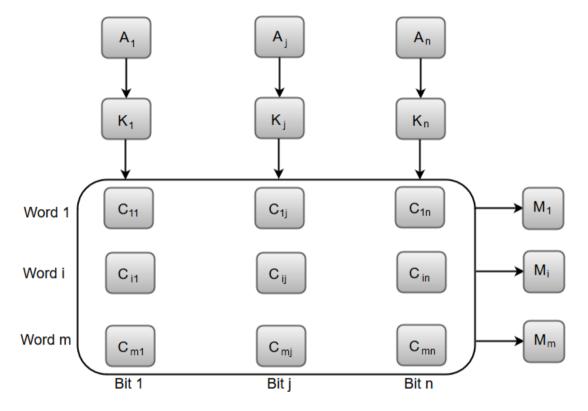

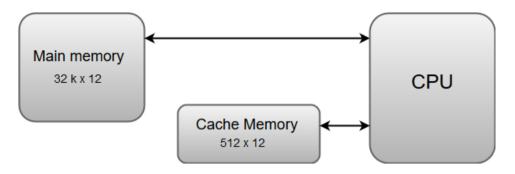

Memory Hierarchy, Main memory, Auxiliary Memory, Associate Memory, Cache Memory and Virtual Memory.

### **Text Books:**

- 1.Computer System Architecture, M.Morris Mano, Prentice Hall of India Pvt.ltd. Third Edition, Sept. 2008.

- 2. B. Ram, "Fundamentals of Microprocessors and Microcomputers", Dhanpat Rai Publications.

### **Reference Books:**

- 1.Computer Architecture and Organization, William Stallings, PHI Pvt. Ltd. Eastern Economy Edition, Sixth Edition, 2003.

- 2.Computer System Architecture John P. Hayes.

## **UNIT 1: DIGITAL LOGICAL CIRCUITS**

## What is Digital Computer? OR Explain the block diagram of digital computers.

- Digital computer is a digital system that performs various computational tasks.

- The word "DIGITAL" implies that the information in the computer is represented by digits.

- Digital computers use the binary number system, which has two digits, 0 and 1.

- A binary digit is called a bit.

- Information is represented in digital computers in the groups of bit.

- By using various coding techniques, groups of bits can be made to represent not only binary numbers but also other symbols, letters of alphabets and decimal digit.

- Bits are grouped together as *bytes* and *words* to form some type of representation within the computer.

- A sequence of instructions for the computer is known as program.

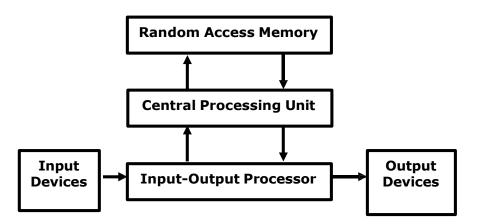

### Block diagram of a digital computer

- The hardware of the computer is usually divided into three major parts.

- The Central processing Unit (CPU) contains an arithmetic and logic unit for manipulating data, a number of registers for storing data and control circuits for fetching and executing instructions.

- The memory of a computer contains storage for instructions and data, it is called a Random Access Memory (RAM) because the CPU can access any location in memory at random and retrieve the binary information within a fixed interval of time.

- The input and output processor contains electronic circuit for communication and controlling the transfer of information between the computer and the outside world.

- The input and output device connected to the computer include keyboards, printers, terminals, magnetic disk drives and other communication devices.

## What is Gates? Explain the Logic Gates in brief.

- Binary information is represented in digital computers using electrical signals.

- These signals can be represented by voltage to specify one of two possible states.

- The two states represent a binary variable that can be equal to 1 or 0.

- The manipulation of binary information in a computer is done using logic circuits called *gates*.

- Gates are blocks of hardware that produce signals of binary 1 or 0 when input logic requirements are satisfied.

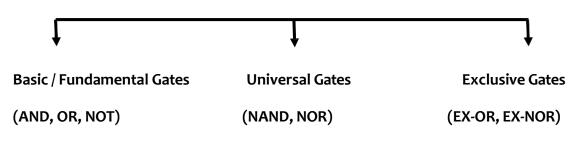

- There are various types of logic gates are commonly used in digital computer.

- Each gate has a different graphic symbols and operation.

- The input-output relationship of binary variables for each gate can be represented in tabular form by Truth-Table.

- There are three types of gates:

- Basic / Fundamental Gates (AND, OR, NOT)

- Universal Gates (NAND, NOR)

- Exclusive Gates (EX-OR, EX-NOR)

### LOGICAL GATES

### **Basic Gates**

### AND Gate:

- In this type of gate output is high only when all its inputs are high.

- If any single input is law then the output will remain low.

- So it is said that in AND gate the output is only high when the input is also high.

### SYMBOL:

### TRUTH-TABLE:

| INPU | JT | OUTPUT  |

|------|----|---------|

| Α    | В  | A AND B |

| 0    | 0  | 0       |

| 0    | 1  | 0       |

| 1    | 0  | 0       |

| 1    | 1  | 1       |

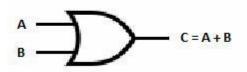

### **OR Gate:**

- In this type of gate if any input signal is high then the output will be high.

- The output is only low only when all the inputs are low

### SYMBOL:

### TRUTH-TABLE:

| INPL | Л | OUTPUT |

|------|---|--------|

| Α    | В | A OR B |

| 0    | 0 | 0      |

| 0    | 1 | 1      |

| 1    | 0 | 1      |

| 1    | 1 | 1      |

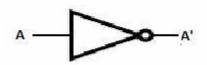

## **NOT Gate:**

- This type of gate is also known as "Inverter".

- It is a gate that contains only one input and only one output.

- The output is always opposite than the input signals.

### SYMBOL:

### TRUTH-TABLE:

| INPUT | OUTPUT        |

|-------|---------------|

| A     | NOT A<br>(A') |

| 0     | 1             |

| 1     | 0             |

### **Universal Gates**

NAND and NOR gates are known as universal gates because we can construct any gate using NAND & NOR gate.

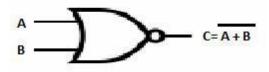

### NOR Gate:

- The NOR gate is the complement of the OR gate.

- As shown in the truth table that the output of NOR gate is exactly opposite than the output of OR gate.

- This means that the output will be high when all the input is low.

### SYMBOL:

### TRUTH-TABLE:

| INP | UT | OUTPUT  |

|-----|----|---------|

| Α   | В  | A NOR B |

| 0   | 0  | 1       |

| 0   | 1  | 0       |

| 1   | 0  | 0       |

| 1   | 1  | 0       |

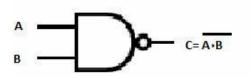

### NAND Gate:

- The NAND gate is an AND gate followed by NOT gate.

- As shown in the truth table that the output of NAND gate is exactly opposite than the output of AND gate.

- This means that the output will be high when all the input is high.

### SYMBOL:

### TRUTH-TABLE:

| INPU | JT | OUTPUT   |

|------|----|----------|

| Α    | В  | A NAND B |

| 0    | 0  | 1        |

| 0    | 1  | 1        |

| 1    | 0  | 1        |

| 1    | 1  | 0        |

### **Exclusive Gates**

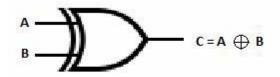

### **EX-OR Gate:**

- This gate is produces high output whenever the two inputs are at opposite level.

- The EX-OR gate is the gate that produces high output for Odd number of high inputs.

### SYMBOL:

### TRUTH-TABLE:

| INPU | JT | OUTPUT    |

|------|----|-----------|

| Α    | В  | A EX-OR B |

| 0    | 0  | 0         |

| 0    | 1  | 1         |

| 1    | 0  | 1         |

| 1    | 1  | 0         |

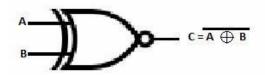

### **EX-NOR Gate:**

- This gate is produces high output whenever the two inputs are at same level.

- The EX-OR gate is the gate that produces high output for Even number of high inputs.

- The truth table shows that output of this gate is exactly opposite of EX-OR gate.

### SYMBOL:

### TRUTH-TABLE:

| INPU | JT | OUTPUT     |

|------|----|------------|

| Α    | В  | A EX-NOR B |

| 0    | 0  | 1          |

| 0    | 1  | 0          |

| 1    | 0  | 0          |

| 1    | 1  | 1          |

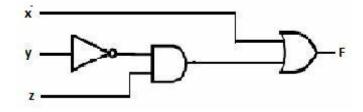

### Write a note on Boolean Algebra

- In 1854 George Boole introduced a systemic treatment of logic and developed for this purpose an algebric system called Boolean Algebra.

- Boolean Algebra is an algebra that deals with binary variables and logic operations.

- The variables are designated by letters such as A, B, X, Y etc.

- The three basic operations are AND, OR and complement.

- A Boolean function can be expressed with binary variable, the logic operation symbols, parentheses (rounded bracket) and equal to (=) sign.

- The result of a Boolean function is either 0 or 1.

- A Boolean function can be represented by either:

- a. Truth tables

- b. Logic diagrams

- c. Algebraic expression

- For example: F=x+y'z

- F=1 only if x is 1 or if both y' and z=1.

- If y'(complement of y)=1 means that y=0 so we can say that F=1 only when x=1,y=0,z=1.

- $_{\odot}$  So we can say that function F equal to 1 for those combination where x=1 or yz=01

- A Boolean function can be transformed form algebraic expression into a logic diagram composed of AND,OR and NOT gates.

- Truth table and logic diagram For above example :

| х | Υ | z | F |

|---|---|---|---|

| 0 | 0 | 0 | 0 |

| 0 | 0 | 1 | 1 |

| 0 | 1 | 0 | 0 |

| 0 | 1 | 1 | 1 |

| 1 | 0 | 0 | 1 |

| 1 | 0 | 1 | 1 |

| 1 | 1 | 0 | 1 |

| 1 | 1 | 1 | 1 |

### **Boolean Operations**

There are three basic logical operations:

- AND: This operation is represented by a dot or by the absence of an operator. For example, x.y = z or xy = z is read "x AND y is equal to z." The logical operation AND is interpreted to mean that z=1 if and only if x=1 and y=1; otherwise z=0.

- OR: This operation is represented by a plus sign. For example, x+y = z is read "x OR y is equal to z", meaning that z=1 if x=1 or if y=1 or if both x=1 and y=1. If both x=0 and y=0, then z=0.

- NOT: This operation is represented by a prime (sometimes by a bar). For example, x' = z (or x = z) is read "x not is equal to z", meaning that z is complement of x. In other words, if x=1, then z=0, but if

- x=0, then z=1.

## **Basic Identities of Boolean Algebra**

### Postulates and theorems of Boolean Algebra

| (a) $x + 0 = x$                 | (b) $x \cdot 1 = x$           |

|---------------------------------|-------------------------------|

| (a) $x' + x' = 1$               | (b) $x \cdot x' = 0$          |

| (a) $x + x = x$                 | (b) $x \cdot x = x$           |

| (a) $x + 1 = 1$                 | (b) $x \cdot 0 = 0$           |

| (x')' = x                       | 2)<br>Decores                 |

| (a) $x + y = y + x$             | (b) $xy = yx$                 |

| (a) $x + (y + z) = (x + y) + z$ | (b) $x(yz) = (xy)z$           |

| (a) $x(y + z) = xy + xz$        | (b) $x + yz = (x + y)(x + z)$ |

| (a) $(x + y)' = x'y'$           | (b) $(xy)' = x' + y'$         |

| (a) $x + xy = x$                | (b) $x(x + y) = x$            |

## Write a note on DeMorgan's theorem

- It is developed greater mathematician and logician named De-Morgan.

- He developed two theorems which makes the complement of questions and product( incomplete line).

- It is very important in dealing with NOR and NAND gates.

- The 2 most important theorems of De-Morgan are as follows:

1) The complement of sum equal to the product of the complement.

x + y = x · y

2) The complement of product equal to the sum of the complement.

$$\overline{\mathbf{x} \cdot \mathbf{y}} = \overline{\mathbf{x}} + \overline{\mathbf{y}}$$

- We can prove the theorems with the help of truth table.

- THEOREM 1:  $\overline{x + y} = \overline{x} \cdot \overline{y}$

| x | У           | x' | y' | (x+y) | (x+y)' | x'. y' |

|---|-------------|----|----|-------|--------|--------|

| 0 | 0           | 1  | 1  | 0     | 1      | 1      |

| 0 | <b>(1</b> ) | 1  | 0  | 1     | 0      | 0      |

| 1 | 0           | 0  | 1  | 1     | o      | o      |

| 1 | 1           | 0  | 0  | 1     | 0      | 0      |

Last 2 columns gives same output so LHS=RHS

THEOREM 2:  $x \cdot y = x + y$

| JREN | 1 2. |    | • y = | хт у  |        | 2       |

|------|------|----|-------|-------|--------|---------|

| x    | у    | x' | y'    | (x.y) | (x.y)' | x' + y' |

| 0    | 0    | 1  | 1     | 0     | 1      | 1       |

| 0    | 1    | 1  | 0     | 0     | 1      | 1       |

| 1    | 0    | 0  | 1     | 0     | 1      | 1       |

| 1    | 1    | 0  | 0     | 1     | 0      | 0       |

• Last 2 columns gives same output so LHS=RHS

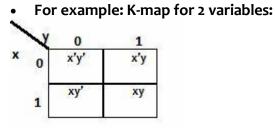

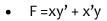

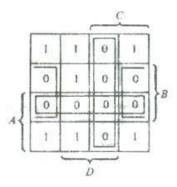

## Write a note on K- Maps.

- The Karnaugh map is also referred as Veitch Diagrams, KV maps or K-maps.

- K-map is a method to minimizes the Boolean function.

- K-map provides a simple and straight forward method to minimizing Boolean expression.

- With the help of K-map we can simplified Boolean expression up to 4 and 6 variables.

- K-map diagram represents squares and each square represents 1 minterm.

- In K-map values of the variables are written in binary form & the logic function can be expressed in one of the following form

- SUM OF PRODUCTS (SOP)

- PRODUCT OF SUM (POS)

- A K-map for n variables is made up of **2**<sup>n</sup> squares and each squares designed a product term of Boolean expression.

- For product terms which are present in expression, 1s are written in correspondence squares and o will be written in blank square.

| k        | - map for a | 3 variable | 25    |

|----------|-------------|------------|-------|

| yz<br>00 | 01          | 11         | 10    |

| x'y'z    | x'y'z       | x'yz       | x'yz' |

| xy'z'    | xy'z        | xyz        | xyz'  |

k-map for 4 variables

| 1  | 00      | 01      | 11     | 10     |

|----|---------|---------|--------|--------|

| 00 | w'x'y'z | w'x'y'z | w'x'yz | w'x'yz |

| 01 | w'xy'z  | w'xy'z  | w'xyz  | w'xyz' |

| 11 | wxy'z'  | wxy'z   | wxyz   | wxyz'  |

| 10 | wx'y'z' | wx'y'z  | wx'yz  | wx'yz' |

### • RULES FOR K- MAP:

- Each cell with 1 must be included in at list 1 group.

- Try to form the largest possible groups.

- Try to end up with as few groups as possible.

- Groups may be in sizes that are powered of 2.

- Groups may be square or rectangular only.

- Groups may be horizontal or vertical but not diagonal.

- Groups may wrap around the table.

- Groups may overleap.

- The larger a group is, the more redundant inputs there are:

- Group of 1 has no redundant input.

- Group of 2 known as pair has 1 redundant input.

- Group of 4 known as quad has 2 redundant input.

- Group of 8 known as octet has 3 redundant input.

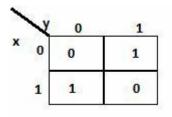

## Sum-of-Products Simplification

- A Boolean function represented by a truth table is plotted into the map by inserting 1's into those squares where the function is 1.

- Boolean functions can then be simplified by identifying adjacent squares in the Karnaugh map that contain a 1.

- A square is considered adjacent to another square if it is next to, above, or below it. In addition, squares at the extreme ends of the same horizontal row are also considered

adjacent. The same applies to the top and bottom squares of a column. The objective to identify adjacent squares containing 1's and group them together.

- Groups must contain a number of squares that is an integral power of 2.

- Groups of combined adjacent squares may share one or more squares with one or more groups.

- Each group of squares represents an algebraic term, and the **OR** of those terms gives the simplified algebraic expression for the function.

- To find the most simplified algebraic expression, the goal of map simplification is to identify the least number of groups with the largest number of members.

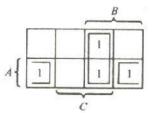

We will simplify the Boolean function. F (A,B,C) =  $\Sigma(3,4,6,7)$

- The three variable maps for this function is shown in the figure 2.4

- There are four squares marked with 1's, one for each minterm that produces 1 for the function. These squares belong to minterm 3,4,6,7 and are recognized from the figure b.

- Two adjacent squares are combined in the third column. This column belongs to both B and C produces the term BC.

- The remaining two squares with 1's in the two corner of the second row are adjacent and belong to row columns of C', so they produce the term AC'.

- The simplified expression for the function is the or of the two terms:

F = BC + AC'

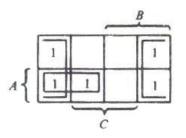

The second example simplifies the following Boolean function:

$$F(A,B,C) = \Sigma (0,2,4,5,6)$$

- The five minterms are marked with 1's in the corresponding squares of the three variable maps.

- The four squares in the first and the fourth columns are adjacent and represent the term C'.

- The remaining square marked with a 1 belongs to minterm 5 and can be combined with the square of minterm 4 to produce the term AB'.

The simplified function is F = C' + AB'

Map for  $F(A,B,C) = \Sigma(0,2,4,5,6)$

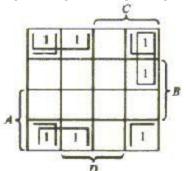

Figure 2.6 Map for  $F(A,B,C,D) = \Sigma(0,1,2,6,8,9,10)$

- The area in the map covered by this four variable consists of the squares marked with 1's in fig 1.10. The function contains 1's in the four corners that when taken as groups give the term B'D'. This is possible because these four squares are adjacent when the map is considered with the top and bottom or left and right edges touching.

- The two 1's on the bottom row are combined with the two 1's on the left of the bottom row to give the term B'C'.

- The remaining 1 in the square of minterm 6 is combined with the minterm 2 to give the term A'CD'.

The simplified function is: F = B'D' + B'C' + A'CD'

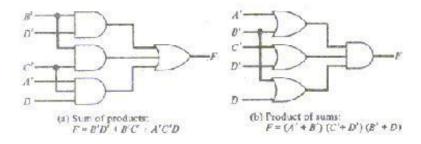

## **Product-of-Sums Simplification**

- Another method for simplifying Boolean expressions can be to represent the function as a product of sums.

- This approach is similar to the Sum-of-Products simplification, but identifying adjacent squares containing o's instead of 1's forms the groups of adjacent squares.

- Then, instead of representing the function as a sum of products, the function is represented as a product of sums.

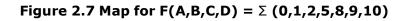

Examples  $F(A,B,C,D) = \Sigma (0,1,2,5,8,9,10)$

The 1's marked in the map of figure 2.7 represents the minterms that produces a 1 for the function.

The squares marked with o's represent the minterm not included in F and therefore denote the complement of F.

Combining the squares with 1's gives the simplified function in sum-of-products form: F = B'D + B'C' + A'C'D

If the squares marked with o's are combined as shown in the diagram, we obtain the simplified complement function:

F'=(A'+B')(C'D')(B'+D)

The logic diagram of the two simplified expression are shown in fig 2.8

### Logic Diagram with AND and OR gates

- The sum of product expression us implemented in fig 2.8(a) with a group of of AND gates, one for each AND term.

- The output of the AND gates are connected to the inputs of a single OR gate. The same function is implemented in fig 2.8(b) in product of sum form with a group of OR gates, one for each OR term, the outputs of the OR gates are connected to the inputs of a single And gate.

- In each case it is assumed that the input variable are directly available in their complement, so inverter are not included.

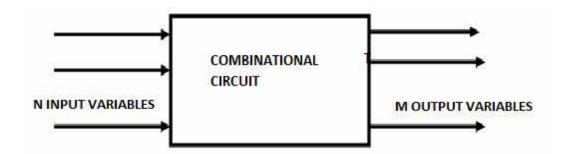

## Write a note on Combinational Circuits

- A combinational circuit is the circuit where more than 1 circuit is designed into single component.

- It has N no of inputs and M no of outputs.

- It is basically used to design digital applications and it transforms the data into the digital manner.

- A combinational circuit is a connected arrangement of logic gates with a set of inputs and outputs.

- At any given time, the binary values of the outputs are a function of the binary values of the inputs.

- The design of a combinational circuit starts from a verbal outline of the problem and ends in a logic circuit diagram. The procedure involves the following steps:

- 1. The problem is stated.

- 2. The input and output variables are assigned letter symbols.

- 3. The truth table that defines the relationship between inputs and outputs is derived.

- 4. The simplified Boolean functions for each output are obtained.

- 5. The logic diagram is drawn.

## **Arithmatic circuits:**

• It is made of different arithmetic operators. There will be addition, substraction, division, modules and any other arithmetic operations.

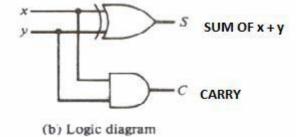

## Half-Adder

- Half-Adder is a part of combinational circuit.

- It is basically designed for arithmetic addition.

- It is most basic digital arithmetic circuit.

- Performs the addition of two binary digits.

- The input variables of a half-adder are called the *augend* and the *addend*.

- The output variables of a half-adder are called the sum and the carry.

| INF | DUT | OUT | PUT   |

|-----|-----|-----|-------|

| x   | Y   | SUM | CARRY |

| 0   | 0   | 0   | 0     |

| 0   | 1   | 1   | 0     |

| 1   | 0   | 1   | 0     |

| 1   | 1   | 0   | 1     |

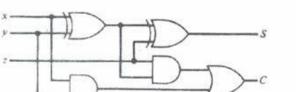

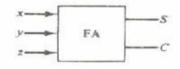

## Full-Adder

- A full-adder performs the addition of three binary digits.

- Two half-adders can be combined to for a full-adder..

- Although a full adder has three inputs, it still only has two outputs since the largest number is 1+1+1 = 3, and 3 can be represented by two bits.

#### TRUTH TABLE OF FULL - ADDER

|   | INPUT |   | OUT             | PUT   |

|---|-------|---|-----------------|-------|

| X | Y     | Z | SUM OF<br>X+Y+Z | CARRY |

| 0 | 0     | 0 | 0               | 0     |

| 0 | 0     | 1 | 1               | 0     |

| 0 | 1     | 0 | 1               | 0     |

| 0 | 1     | 1 | 0               | 1     |

| 1 | 0     | 0 | 1               | 0     |

| 1 | 0     | 1 | 0               | 1     |

| 1 | 1     | 0 | 0               | 21    |

| 1 | 1     | 1 | 1               | 1     |

LOGIC DIAGRAM OF FULL - ADDER

## WHAT IS THE DIFFERENCE BETWEEN HALF ADDER AND FULL ADDER?

| Half adder                                   | Full adder                                  |

|----------------------------------------------|---------------------------------------------|

| The most basic digital arithmetic circuit.   | A full-adder performs the addition of three |

|                                              | binary digits.                              |

| Performs the addition of two binary digits.  | It is used for multi bit additions.         |

| Output is sum of two signals.                | Output is sum of three signals.             |

| There are two input and two output           | There are three input and two output        |

| terminal.                                    | terminal.                                   |

| From full adder half adder cant not be built | Two full adder makes one full adder         |

| On EX-OR gate and one AND gate are used.     | Two EX-OR, two AND and one OR gate is       |

|                                              | used.                                       |

## WHAT IS THE DIFFERENCE BETWEEN COMBINATIONAL CIRCUIT AND SEQUENCIAL CIRCUIT?

| <b>COMBINATIONAL CIRCUIT</b>                                                                                                 | SEQUENTIAL CIRCUIT                                                                                                                         |  |  |  |  |

|------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| It is a digital logic circuit whose output depends on the present inputs.                                                    | It is a digital logic circuit whose output<br>depends on the present inputs as well as<br>previous inputs.                                 |  |  |  |  |

| It can describe by the output values.                                                                                        | It can describe by the output values as well as state values.                                                                              |  |  |  |  |

| It contains no memory element.                                                                                               | It contains at least one memory element.                                                                                                   |  |  |  |  |

| It is easy to design and understand.                                                                                         | It is difficult to design and understand.                                                                                                  |  |  |  |  |

| It is faster in speed.                                                                                                       | It is slower in speed.                                                                                                                     |  |  |  |  |

| It is expensive in cost.                                                                                                     | It is less expensive in cost.                                                                                                              |  |  |  |  |

| Examples of combinational circuit are half adder and full adder.                                                             | Examples of sequential circuit are flip-flops<br>like RS, Clocked RS, D and JK.                                                            |  |  |  |  |

| A combinational circuit is a connected arrangement of logic gates with a set of inputs and outputs.                          | However, if a circuit uses both gates and flip-flops, it is called a sequential circuit.                                                   |  |  |  |  |

| At any given time, the binary values of the outputs are a function of the binary values of the inputs.                       | Hence, a sequential circuit is an interconnection of flip-flops and gates.                                                                 |  |  |  |  |

| The design of a combinational circuit starts<br>from a verbal outline of the problem and<br>ends in a logic circuit diagram. | If we think of a sequential circuit as some<br>black box that, when provided with some<br>external input, produces some external<br>output |  |  |  |  |

## What is Flip-flops

- A Flip-flop is a binary cell capable of storing one bit of information.

- It has two outputs, one for the normal value and one for the complement value of the bit stored in it.

- Flip-flops are storage elements utilized in synchronous sequential circuits.

- Synchronous sequential circuits employ signals that effect storage elements only at discrete instances of time.

- A timing device called a clock pulse generator that produces a periodic train of clock pulses achieves synchronization.

- Values maintained in the storage elements can only change when the clock pulses.

- Hence, a flip-flop maintains a binary state until directed by a clock pulse to switch states.

- The difference in the types of flip flops is in the number of inputs and the manner in which the inputs affect the binary state.

- Flip-flops can be described by a *characteristic table* which permutates all possible inputs (just like a truth table).

- The characteristic table of a flip-flop describes all possible outputs (called the *next* state) at time Q(t+1) over all possible inputs and the *present state* at time Q(t).

- The most common types of flip flops are:

- SR Flip-Flop

- D Flip-Flop

- JK Flip-Flop

- T Flip-Flop

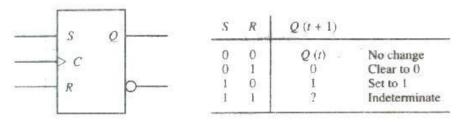

## **SR Flip-Flop**

### Figure SR Flip-Flop

(a) Graphic symbol

(b) Characteristic table

Inputs:

- S (for set)

- R (for reset)

- C (for clock)

Outputs:

- Q

- Q'

The operation of the SR flip-flop is as follow.

- If there is no signal at the clock input C, the output of the circuit cannot change irrespective of the values at inputs S and R.

- Only when the clock signals changes from 0 to 1 can the output be affected according to the values in inputs S and R

- If S =1 and R = 0 when C changes when C changes from 0 to 1 output Q is set to 1. If S = 0 and R =1 when C changes from 0 to 1.

- If both S and R are o during the clock transition, output does not change.

- When both S and R are equal to 1, the output is unpredictable and may go to either o or 1, depending on internal timing that occur within the circuit.

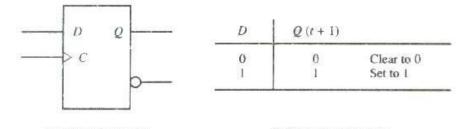

## D Flip-Flop

### D Flip-flop

(a) Graphic symbol

(b) Characteristic table

Inputs:

- D (for data)

- C (for clock)

Outputs:

- Q

- Q'

The operation of the D flip-flop is as follow.

- The D Flip-Flop can be converted from SR Flip-Flop by inserting an inverter between S and R and assigning the symbol D to the single input.

- The D input is sampled during the occurrence of a clock transition from 0 to 1.

- If D=1, the output of the flip-flop goes to the 1 state, but if D=0, the output of the flip-flop goes to the 0 state.

- The next state Q(t+1) is determined from the D input. The relationship can be expressed by a characteristic equation:

Q(t+1) = D

D Flip-Flop has the advantage of having only one input (excluding ), but the disadvantage that its characteristic table does not have a "no change" condition Q(t+1) = Q(t).

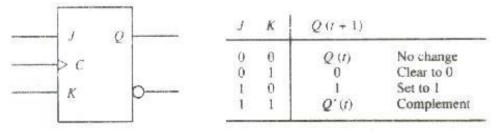

## **JK Flip-Flop**

## Jk Flip-Flop

(a) Graphic symbol

(b) Characteristic table

Inputs:

- J

- K

- C (for clock)

Outputs:

- Q

- Q'

The operation of the JK flip-flop is as follow.

- A JK Flip-Flop is a refinement of the SR flip-flop in that the indeterminate condition of the SR type is defined in the JK type.

- Inputs J and K behave like inputs S and R to set and clear the flip-flop, respectively.

- When inputs J and K are both equal to 1, a clock transition switches the outputs of the flip-flop to their complement state.

- Instead of the indeterminate condition of the SR flip-flop, the JK flip-flop has a complement condition Q(t+1) = Q'(t) when both J and K are equal to 1.

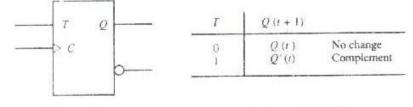

## T Flip-Flop

### T Flip-Flop

(a) Graphic symbol

(b) Characteristic table

Inputs:

- T (for toggle)

- C (for clock)

Outputs:

- Q

- Q'

The operation of the T flip-flop is as follow.

- Most flip-flops are edge-triggered flip-flops, which means that the transition occurs at a specific level of the clock pulse.

- A positive-edge transition occurs on the rising edge of the clock signal.

- A negative-edge transition occurs on the falling edge of the clock signal.

- Another type of flip-flop is called a master-slave flip-flop that is basically two flip-flops in series.

- Flip-flops can also include special input terminals for setting or clearing the flip-flop *asynchronously*. These inputs are usually called *preset* and *clear* and are useful for initialing the flip-flops before *clocked* operations are initiated.

## **Flip-Flop Excitation Tables**

- During the design of sequential circuits, the required transition from present state to next state is known.

- What the designer needs to know is what input conditions must exist to implement the required transition.

- This requires the use of flip-flop excitation tables.

### **Excitation Tables**

|      | SR Flip-Flop Excitation Table |   |   |  |  |  |  |

|------|-------------------------------|---|---|--|--|--|--|

| Q(t) | Q(t+1)                        | S | R |  |  |  |  |

| 0    | 0                             | 0 | x |  |  |  |  |

| 0    | 1                             | 1 | 0 |  |  |  |  |

| 1    | 0                             | 0 | 1 |  |  |  |  |

| 1    | 1                             | х | 0 |  |  |  |  |

|      | JK Flip-Flop Excitation Table |   |   |  |  |  |  |

|------|-------------------------------|---|---|--|--|--|--|

| Q(t) | Q(t+1)                        | J | К |  |  |  |  |

| 0    | 0                             | 0 | х |  |  |  |  |

| 0    | 1                             | 1 | Х |  |  |  |  |

| 1    | 0                             | Х | 1 |  |  |  |  |

| 1    | 1                             | Х | 0 |  |  |  |  |

| -    | T Flip-Flop Excitation Table |   |  |  |  |  |  |

|------|------------------------------|---|--|--|--|--|--|

| Q(t) | Q(t+1)                       | Т |  |  |  |  |  |

| 0    | 0                            | 0 |  |  |  |  |  |

| 0    | 1                            | 1 |  |  |  |  |  |

| 1    | 0                            | 1 |  |  |  |  |  |

| 1    | 1                            | 0 |  |  |  |  |  |

## **Sequential Circuits**

- When a circuit contains just gates, it is called a *combinational* circuit. However, if a circuit uses both gates and flip-flops, it is called a *sequential* circuit. Hence, a sequential circuit is an interconnection of flip-flops and gates.

- If we think of a sequential circuit as some *black box* that, when provided with some *external* input, produces some *external* output, a typical sequential circuit would function as follows:

- The *external* inputs constitute *some* of the inputs to the combinational circuit. The *internal* outputs of the combinational circuit are the *internal* inputs to the flip-flops.

- The *internal* outputs of the flip-flops constitute the remaining inputs to the combinational circuit. The *external* outputs are some combination of the outputs from the combinational circuit and flip-flops. The behavior of a sequential circuit is determined from the inputs, the outputs, and the state of the flip-flops. Both the outputs and the next state are determined by the inputs and the present state.

- A state diagram can represent the information in a state table graphically, where states are represented by circles (vertices) and transitions on specific input is represented by the *labels* on the directed lines (edges) connecting the circles.

### **Design Procedure**

- Formulate behavior of circuit using a state diagram.

- Determine # of flip-flops needed (equal to # bits in circles).

- Determine # inputs (specified on edges of diagram).

- Create state table, assigning letters to flip-flips, input, and output variables.\*

- For each row, list the next state as specified by the state diagram.

- Select flip-flop type to be used in circuit.

- Extend state table into an excitation table by including columns for each input of each flip-flop.

- Using excitation table and present state-to-next state transitions, formulate input conditions for flip-flops.

- Construct truth table for combinational circuit using present-state and input columns of excitation table (for inputs) and flip-flop inputs (for outputs).

- Use map simplification of truth table to obtain flip-flop input equations.\*\*

- Determine *external* outputs of sequential circuit (flip-flop outputs and potentially combinational circuit outputs).

- Draw logic diagram as follows:

- Draw flip-flops and label all their inputs and outputs.

- Draw combinational circuit from the Boolean expressions given by the flipflop input equations.

- Connect outputs of flip-flops to inputs in the combinational circuit.

- Connect outputs of combinational circuit to flip-flop inputs.

For *m* flip-flops and *n* inputs, the state table will consist of *m* columns for the present state, *n* columns for the inputs, and *m* columns for the next state. The number of rows in the table will be up to 2m+n, one row for each binary combination of present state and inputs.

\*\* Each flip-flop input equation specifies a logic diagram whose output must be connected to one of the flip-flop inputs.

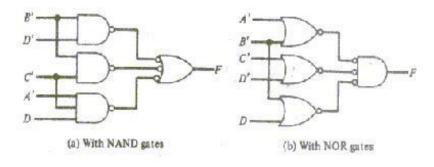

### NAND and NOR Implementation

A sum-of-products expression can be implemented with NAND and NOR gates as shown in the figure 2.9

### Figure 2.9 Logic Diagram with NAND and NOR gates

### **Don't Care Conditions**

- In k-map each cell represents a minterm or maxterm and the o's and 1's in k map represents the minterm that make the function equal to either 0 or 1.

- But in some occasion, it doesn't matter whether a function produces a 0 or 1 for a given minterm.

- When this condition occurs, an X is used in the map to represent the *don't care* condition.

- The minterm that may produce either 0 or 1 for function are said to be Don't Care and marked as x in map.

- This don't care condition are used to further simplify the Boolean expression.

- Don't care condition is the condition where any single square or map will appear as x n it is not necessary to write into Boolean expression.

## Example

$F(w,x,y,z) = \sum (0,1) + d(4,5,14)$

| $\mathbf{\mathbf{Y}}$ | 00 | 01 | 11  | 10 |

|-----------------------|----|----|-----|----|

| 00                    | 1. | 1  | 2.5 |    |

| 01                    | x  | x  |     |    |

| 1                     | 1  |    | 8   |    |

| 11                    |    |    |     | x  |

| 10                    |    |    |     |    |

• So the ans is **W'Y'**

## **UNIT 2: DIGITAL COMPONENTS**

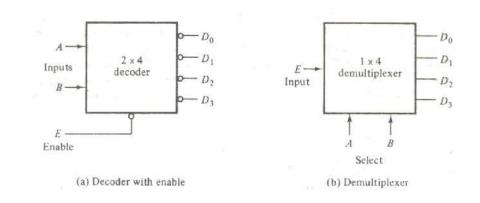

## What is Decoder?

- Discrete quantities of information are represented in digital computers with binary codes.

- A binary code of n bits is capable of representing up to 2n distinct elements of the coded information.

- A decoder is a combinational circuit that converts binary information from the n coded inputs to a maximum of 2n unique outputs.

- If the n-bit coded information has unused bit combinations, the decoder may have less than 2n outputs.

- The decoders presented in this section are called n-to-m-line decoders, where m <= 2n. Their purpose is to generate the 2n (or fewer) binary combinations of the n input variables. A decoder has n inputs and m outputs and is also referred to as an n x m decoder.

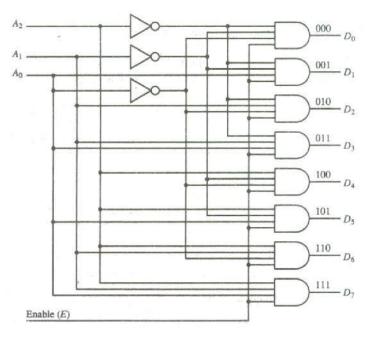

- The logic diagram of a 3-to-8-line decoder is shown bellow.

- The three data inputs. Ao, A1, and A2, are decoded into eight outputs, each output representing one of the combinations of the three binary input variables.

- The three inverters provide the complement of the inputs, and each of the eight AND gates generates one of the binary combination.

- A particular application of this decoder is a binary-to-octal conversion. The input variables represent a binary number and the outputs represent the eight digits of the octal number system.

- However, a 3-to-8-line decoder can be used for decoding any 3-bit code to provide eight outputs, one for each combination of the binary code.

- Commercial decoders include one or more enable inputs to control the operation of the circuit. The decoder of the Figure has one enable input, E.

- The decoder is enabled when E is equal to 1 and disabled when E is equal to 0. The operation of the decoder can be clarified using the truth table listed in Table.

- When the enable input E is equal to o, all the outputs are equal to o regardless of the values of the other three data inputs.

- The three x's in the table designate don't-care conditions. When the enable input is equal to 1, the decoder operates in a normal fashion.

- For each possible input combination, there are seven outputs that are equal to 0 and only one that is equal to 1.

- The output variable whose value is equal to 1 represents the octal number equivalent of the binary number that is available in the input data lines.

| Enable |                  | Inputs |                |    |       |       | Out   | puts  |       |       |    |

|--------|------------------|--------|----------------|----|-------|-------|-------|-------|-------|-------|----|

| E      | $\overline{A_2}$ | $A_1$  | A <sub>0</sub> | D7 | $D_6$ | $D_5$ | $D_4$ | $D_3$ | $D_2$ | $D_1$ | Do |

| 0      | ×                | ×      | ×              | 0  | 0     | 0     | 0     | 0     | 0     | 0     | 0  |

| 1      | 0                | 0      | 0              | 0  | 0     | 0     | 0     | 0     | 0     | 0     | 1  |

| 1      | 0                | 0      | 1              | 0  | 0     | 0     | 0     | 0     | 0     | 1     | 0  |

| 1      | 0                | 1      | 0              | 0  | 0     | 0     | 0     | 0     | 1     | 0     | 0  |

| 1      | 0                | 1      | 1              | 0  | 0     | 0     | 0     | 1     | 0     | 0     | 0  |

| 1.     | 1                | 0      | 0              | 0  | 0     | 0     | 1     | 0     | 0     | 0     | 0  |

| 1      | 1                | 0      | 1              | 0  | 0     | 1     | 0     | 0     | 0     | 0     | 0  |

| 1      | 1                | 1      | 0              | 0  | 1     | 0     | 0     | 0     | 0     | 0     | 0  |

| 1      | í                | 1      | 1              | 1  | 0     | 0     | 0     | 0     | 0     | 0     | 0  |

### Truth Table for 3-to-8-line Decoder

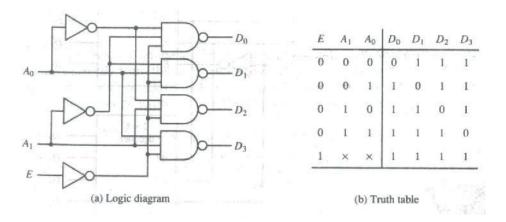

### • NAND Gate Decoder

- Some decoders are constructed with NAND instead of AND gates. Since a NAND gate produces the AND operation with an inverted output, it becomes more economical to generate the decoder outputs in their complement form.

- A 2-to-4-line decoder with an enable input constructed with NAND gates is shown in Figure.

- The circuit operates with complemented outputs and a complemented enable input E. The decoder is enabled when E is equal to o. As indicated by the truth table, only one output is equal to o at any given time; the other three outputs are equal to 1.

- The output whose value is equal to o represents the equivalent binary number in inputs Ai and Ao.

- The circuit is disabled when E is equal to 1, regardless of the values of the other two inputs.

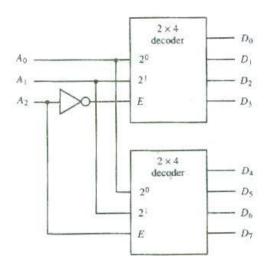

### • Decoder Expansion

• A technique called decoder expansion can be utilized to construct larger decoders out of smaller ones.

• For example, two 2-to-4-line decoders can be combined to construct a 3-to-8-line decoder. Figure below shows 3-8-line decoder constructed with two 2x4 decoders.

### 3X8 decoder constructed with two 2X4 decoders

- The above given Figure shows how the decoders with enable inputs can be connected to form a larger decoder.

- As you can see that there are two 2-to-4-line decoders are combined to achieve a 3-to-8-line decoder.

- The two least significant bits of the input are connected to both decoders.

- The most significant bit is connected to the enable input of one decoder and through an inverter to the enable input of the other decoder.

- It is assumed that each decoder is enabled when its E input is equal to 1. When E is equal to 0, the decoder is disabled and all its outputs are in the 0 level. When A<sub>2</sub> = 0, the upper decoder is enabled and the lower is disabled.

- The lower decoder outputs become inactive with all outputs at o. The outputs of the upper decoder generate outputs Do through D3, depending on the values of A1 and Ao(while A2 = 0).

- When A<sub>2</sub>= 1, the lower decoder is enabled and the upper is disabled. The lower decoder output generates the binary equivalent D<sub>4</sub>, through D<sub>7</sub> since these binary numbers have a 1 in the A<sub>2</sub> position.

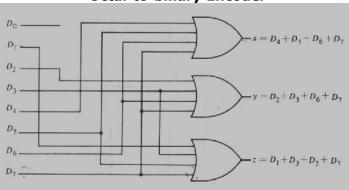

### What is Encoder?

- An encoder is a digital circuit that performs the inverse operation of a decoder. An encoder has 2<sup>n</sup> (or less) input lines and n output lines.

- The output lines generate the binary code corresponding to the input value. An example of an encoder is the octal-to-binary encoder, whose truth table is given below.

| Inpu | ıts |    | out | outs |    |    |    |    |    |    |

|------|-----|----|-----|------|----|----|----|----|----|----|

| D7   | D6  | D5 | D4  | D3   | D2 | D1 | D0 | A2 | A1 | A0 |

| 0    | 0   | 0  | 0   | 0    | 0  | 0  | 1  | 0  | 0  | 0  |

| 0    | 0   | 0  | 0   | 0    | 0  | 1  | 0  | 0  | 0  | 1  |

| 0    | 0   | 0  | 0   | 0    | 1  | 0  | 0  | 0  | 1  | 0  |

| 0    | 0   | 0  | 0   | 1    | 0  | 0  | 0  | 0  | 1  | 1  |

| 0    | 0   | 0  | 1   | 0    | 0  | 0  | 0  | 1  | 0  | 0  |

| 0    | 0   | 1  | 0   | 0    | 0  | 0  | 0  | 1  | 0  | 1  |

| 0    | 1   | 0  | 0   | 0    | 0  | 0  | 0  | 1  | 1  | 0  |

| 1    | 0   | 0  | 0   | 0    | 0  | 0  | 0  | 1  | 1  | 1  |

- The encoder can be implemented with OR gates whose inputs are determined directly from the truth table.

- Output Ao =1 if the input octal digit is 1 or 3 or 5 or 7. Similar conditions apply for other two outputs.

These conditions can be expressed by the following Boolean functions :

Ao = D1 + D3 + D5 + D7 A1 = D2 + D4 + D6 + D7A2 = D4 + D5 + D6 + D7

The encoder can be implemented with three OR gates.

### **Octal-to-binary Encoder**

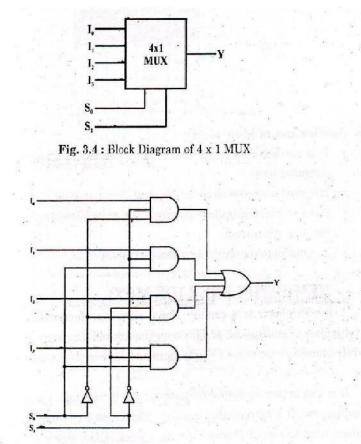

### Write a note on Multiplexer

- A multiplexer is a combinational circuit that receives binary information from one of 2n input data lines and directs it to a single output line.

- The selection of a particular input data line for the output is determined by a set of selection inputs. A 2n-to-1 multiplexer has 2n input data lines and n input selection lines whose bit combinations determine which input data are selected for the output.

- The 4-to-1 line multiplexer has six inputs and one output. A truth table describing the circuit needs 64 rows since six input variables can have 26 binary combinations. This is

an extremely long table and will not be shown here. A more convenient way to describe the operation of multiplexers is by means of a function table.

- The function table for the multiplexer is shown in table.

- The table demonstrates the relationship between the four data inputs and the single output as a function of the selection inputs S1 and So.

| Se | Select |            |  |  |  |

|----|--------|------------|--|--|--|

| S1 | So     | Y          |  |  |  |

| 0  | 0      | lo         |  |  |  |

| 0  | 1      | <b>l</b> 1 |  |  |  |

| 1  | 0      | 12         |  |  |  |

| 1  | 1      | 13         |  |  |  |

#### Function table for 4-to-1 line multiplexer

4-to-1 line Multiplexer

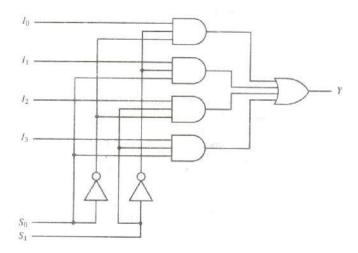

### Write a note on DeMultiplexer

- A decoder with an enable input can function as a demultiplexer.

- A demultiplexer is a circuit that receives information on a single line and transmits this information on one of 2n possible output lines.

- The selection of a specific output line is controlled by the bit values of n selection lines. The decoder of figure a can function as a demultiplexer if the E line is taken as a data input line and lines A and B are taken as the selection lines.

- The single input variable E has a path to all four outputs, but the input information is directed to only one of the output lines, as specified by the binary value of the two selection lines A and B.

- For example, if the selection lines AB = 10; output D2 will be the same as the input value E, while all other outputs are maintained at 1.

- Because decoder and demultiplexer operations are obtained from the same circuit, a decoder with an enable input is referred to as a decoder / demultiplexer.

- It is the enable input that makes the circuit a demultiplexer.

Block Diagram for DeMultiplexer

## **Truth Table Of Demultiplexer**

| Input |           |           |    |           | Output |    |

|-------|-----------|-----------|----|-----------|--------|----|

| D     | <b>S0</b> | <b>S1</b> | FO | <b>F1</b> | F2     | F3 |

| 0     | 0         | 0         | 0  | 0         | 0      | 0  |

| 0     | 0         | 1         | 0  | 0         | 0      | 0  |

| 0     | 1         | 0         | 0  | 0         | 0      | 0  |

| 0     | 1         | 1         | 0  | 0         | 0      | 0  |

| 1     | 0         | 0         | 1  | 0         | 0      | 0  |

| 1     | 0         | 1         | 0  | 1         | 0      | 0  |

| 1     | 1         | 0         | 0  | 0         | 1      | 0  |

| 1     | 1         | 1         | 0  | 0         | 0      | 1  |

### Explain MUX in detail.

- MUX is combinational circuit that is used to direct one out of 2n input data Lines to A single output line.

- It is also known as data selector because it selects one of many inputs And directs it to the output.

- The selection of particular input data line is controlled by as Set of selection inputs.

- Normally there are 2n input data lines and n input selection lines.

- The Block diagram of 4 to 1 line MUX is shown in fig. and logic circuit is displayed in fig.

- Each of the 4 data input Io through I3 is applied to one input of AND gate.

- The two selection inputs s1 and s0 are decoded To select a particular AND gate.

- The output of the AND gates are applied to a single OR gate to provide the single output.

### simplification of Multiplexer.

- It is used to connecting two or more sources to a single destination among computer units.

- It is used in digital circuits to control signal and in data routing.

- It is also useful in operation sequencing.

- It is useful to constructing a common bus system.

### What are Registers? Explain the types of registers.

- A register is a group of flip-flops capable of storing one bit of information.

- An *n*-bit register has a group of *n* flip-flops and is capable of storing any binary information of *n* bits.

- In addition to flip-flops, registers can have combinational gates that perform certain data-processing tasks. The gates control how and when new information is transferred into the registers.

- The transfer of new information into a register is referred to as a *register load*. If the loading occurs simultaneously at a common clock pulse transition, we say that the load is done in *parallel*.

- The load input in a register determines the action to be taken with each clock pulse.

• When the load input is 1, the data from the input lines is transferred into the register's flip-flops. When the load input is 0, the data inputs are *inhibited* and the flip-flop maintains its present state.

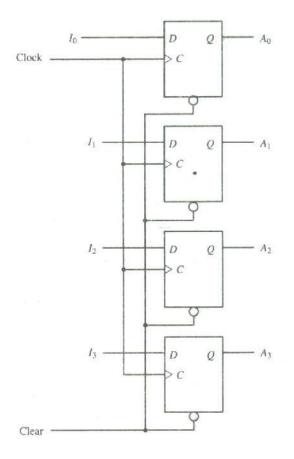

A 4-bit register is shown in the figure below. A clock transition applied to the C inputs of the register will load all four inputs  $I_0$  through  $I_3$  in parallel.

### Figure 5.1 4-bit register

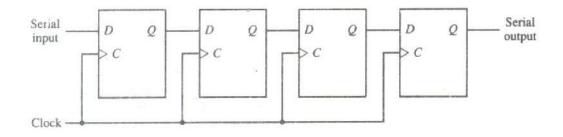

## **Shift Registers**

- A register capable of shifting its binary information in one or both directions is called a shift register.

- Shift registers are constructed by connecting flip-flops in *cascade*, where the output of one flip-flop is connected to the input of the next flip-flop.

- All flip-flops receive common clock pulses that initiate the shift from one stage to the next.

- A serial input shift register has a single external input (called the serial input) entering an outermost flip-flop. Each remaining flip-flop uses the output of the previous flipflop as its input, with the last flip-flop producing the external output (called the serial output).

- A register capable of shifting in one direction is called a *unidirectional* shift register.

- A register that can shift in both directions is called a *bi-directional* shift register.

- The most general shift register has the following capabilities:

- An input for clock pulses to synchronize all operations.

- A shift-right operation and a serial input line associated with the shift-right.

- A shift-left operation and a serial input line associated with the shift-left.

- A parallel load operation and *n* input lines associated with the parallel transfer.

- *N* parallel output lines.

- A control state that leaves the information in the register unchanged even though clock pulses are applied continuously.

- A mode control to determine which type of register operation to perform.

The simplest possible shift register is one that uses only flip-flops, as shown in the figure below.

### 4-bit shift register

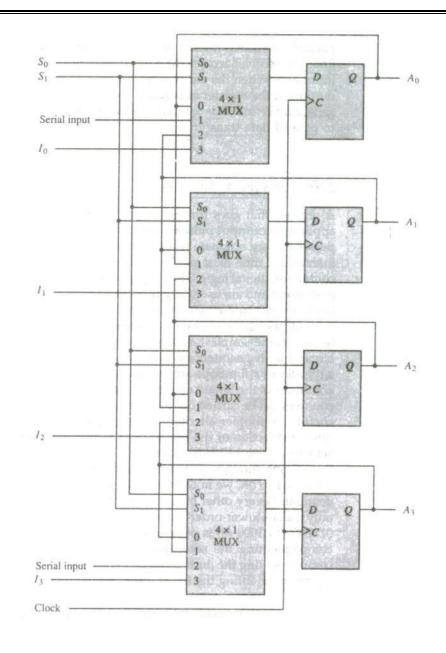

## **Bidirectional Shift Register with parallel load**

- A register that can shift in both directions is called a bi-directional shift register.

- A 4-bit bidirectional shift register with parallel load is shown in figure below. Each stage consists of a D flip-flop and a 4X1 MUX.

- The two selection inputs S1 and S0 select one of the MUX data inputs for the D flipflop. The selection lines control the mode of operation of the register according to the function table shown in table below.

- When the mode control S1S0 = 00, data input 0 of each MUX is selected.

- This condition forms a path from the output of each flip-flop into the input of the same flip-flop.

- The next clock transition refers into each flip-flop the binary value it held previously, and no change of state occurs. When S1S0 = 01, the terminal marked 1 in each MUX has a path to the D input of the corresponding flip-flop.

- This causes a shift-right operation, with the serial input data transferred into flip-flop Ao and the content of each flip-flop Ai-1 transferred into flip-flop Ai for i=1,2,3. When S1So = 10 a shift-left operations results, with the other serial input data going into flip-flop A3 and the content of flip-flop Ai+1 transferred into flip-flop Ai for I=0,1,2. When S1So = 11, the binary information from each input Io through I3 is transferred into the corresponding flip-flop, resulting in a parallel load operation.

- In the diagram, the shift-right operation shifts the contents of the register in the down direction while the shift left operation causes the contents of the register to shift in the upward direction.

### Bidirectional Shift register with parallel load

## **Application of Shift Registers**

- Shift registers are often used to interface digital systems situated remotely from each other. For example, suppose that it is necessary to transmit an n-bit quantity between two points.

- If the distance between the source and the destination is too far, it will be expensive to use n lines to transmit the n bits in parallel.

- It may be more economical to use a single line and transmit the information serially one bit at a time.

- The transmitter loads the n-bit data in parallel into a shift register and then transmits the data from the serial output line.

- The receiver accepts the data serially into a shift register through its serial input line. When the entire n bits are accumulated they can be taken from the outputs of the register in parallel.

- Thus the transmitter performs a parallel-to-serial conversion of data and the receiver converts the incoming serial data back to parallel data transfer.

## UNIT-3

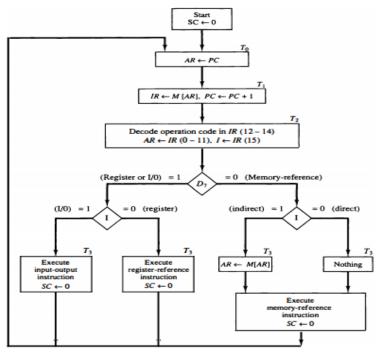

## **Instruction Cycle**

A program residing in the memory unit of the computer consists of a sequence of instructions. The program is executed in the computer by going through a cycle for each instruction. Each instruction cycle in turn is subdivided into a sequence of sub cycles or phases.

In the basic computer each instruction cycle consists of the following phases:

- 1. Fetch an instruction from memory.

- 2. Decode the instruction.

- 3. Read the effective address from memory if the instruction has an indirect address.

- 4. Execute the instruction.

Upon the completion of step 4, the control goes back to step 1 to fetch, decode, and execute the next instruction. This process continues indefinitely unless a HALT instruction is encountered.

### Fetch phase

- Initially, the program counter PC is loaded with the address of the first instruction in the program.

- The sequence counter SC is cleared to 0, providing a decoded timing signal To.

- After each clock pulse, SC is incremented by one, so that the timing signals go through a sequence T0, T1, T2, and so on.

- During  $T_0$  we have to transfer the address from PC to AR.

Figure Flowchart for instruction cycle (initial configuration).

T1:  $IR \leq M[AR]$ ,  $PC \leq PC + 1$

In timing signal  $T_1$  the instruction read from memory is placed in IR,At the same time, PC is incremented by One to prepare it for the address of the next instruction in the program.

## **Decodephase:**

$T_2: D_0....D_7 \qquad \qquad \text{Decode IR}(12-14)$   $AR \qquad \qquad \text{IR}(0-11), I \qquad \qquad \text{IR}(15)$

The operation code in IR is decoded the indirect bit is transferred to flipflop I and address part of the instruction is transferred to AR.

## **Decisionphase:**

During time  $T_{3,}$  the control unit determines the type of instruction that was just read from memory.

$D_7 \rightarrow Decision making$

If  $0 \rightarrow$  then memory reference instruction

If  $1 \rightarrow$  the I/o or register reference instruction

If  $D_7=0$  then opcode code have any value from 000 to 110

D<sub>7</sub>=0 memory reference instruction

If D<sub>7</sub>=0 and I=1

memory reference instruction with an indirect address. It is then necessary to read the effective address from memory

$$AR + M[AR]$$

If D<sub>7</sub>=0 and I=0

not necessary to do anything since effective address is already in AR.

If  $D_7=0$  and  $I=0 \rightarrow \text{Register reference instruction}$

If  $D_7=1$  and  $I=1 \rightarrow$  Input and output instruction

| D' IT 3:      | $AR \leftarrow M[AR]$                    |

|---------------|------------------------------------------|

| D' I'T3:      | Nothing                                  |

| $D_7 I'T_3$ : | Execute a register-reference instruction |

| D7IT3:        | Execute an input-output instruction      |

## **Memory reference instruction**

When D7=0 and I=0

i.e  $D_0$  to  $D_6$  are opcode

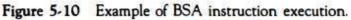

#### **D** $_0 \rightarrow$ **AND to AC**

There is no direct path from bus into accumulator, first the logic receive info from the data register and then transfer. first the contents will be stored in data register and then AND operation will be performed between the bits of the accumulator and that particular data.

> D0T4: DR  $\leftarrow$  M[AR] D0T5: AC  $\leftarrow$  AC  $\land$  DR, SC  $\leftarrow$  0

### **<u>D</u><sub>1</sub> \rightarrow <b>ADD** to **AC**

This instruction adds the content of the memory word specified by the effective address to the value of AC. The sum is transferred into AC and the output carry C,., is transferred to the E (extended accumulator) flip-flop. The microoperations

### $D_2 \rightarrow LDA$ : Load to AC

This instruction transfers the memory word specified by the effective address to AC. The rnicrooperations needed to execute this instruction are

$$D_2T_4: DR \leftarrow M[AR] \\ D_2T_5: AC \leftarrow DR, SC \leftarrow 0$$

Looking back at the bus system shown in Fig. 5-4 we note that there is no direct path from the bus into AC. The adder and logic circuit receive information from DR which can be transferred into AC. Therefore, it is necessary to read the memory word into DR first and then transfer the content of DR into AC. The reason for not connecting the bus to the inputs of AC is the delay encountered in the adder and logic circuit. It is assumed that the time it takes to read from memory and transfer the word through the bus as well as the adder and logic circuit is more than the time of one clock cycle. By not connecting the bus to the inputs of AC we can maintain one clock cycle per microoperation.

### **D<sub>3→</sub>STA: Store AC**

This instruction stores the content of AC into the memory word specified by the effective address. Since the output of AC is applied to the bus and the data input of memory is connected to the bus, we can execute this instruction with one microoperation:

## $D_3T_4$ : $M[AR] \leftarrow AC$ , $SC \leftarrow 0$

#### **D**<sub>4→</sub>**BUN: Branch Unconditionally**

This instruction transfers the program to the instruction specified by the effective address. Remember that PC holds the address of the instruction to be read from memory in the next instruction cycle. PC is incremented at time T1 to prepare it for the address of the next instruction in the program sequence. The BUN instruction allows the programmer to specify an instruction out of sequence and we say that the program branches (or jumps) unconditionally. The instruction is executed with one microoperation:

$D_4T_4$ :  $PC \leftarrow AR$ ,  $SC \leftarrow 0$

The effective address from AR is transferred through the common bus to PC. Resetting SC to 0 transfers control to T0• The next instruction is then fetched and executed from the memory address given by the new value in PC.

### **D5→BSA: Branch and Save Return Address**

This instruction is useful for branching to a portion of the program called a subroutine or procedure. When executed, the BSA instruction stores the address of the next instruction in sequence (which is available in PC) into a memory location specified by the effective address. The effective address plus one is then transferred to PC to serve as the address of the first instruction in the subroutine. This operation was specified in Table 5-4 with the following register transfer:

## $M[AR] \leftarrow PC, PC \leftarrow AR + 1$

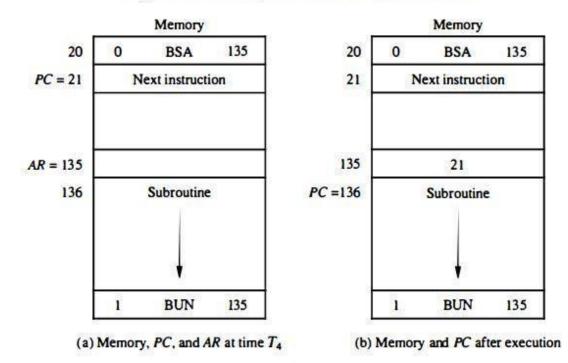

A numerical example that demonstrates how this instruction is used with a subroutine is shown in Fig. 5-10. The BSA instruction is assumed to be in memory at address 20. The I bit is 0 and the address part of the instruction has the binary equivalent of 135. After the fetch and decode phases, PC contains 21, which is the address of the next instruction in the program (referred to as the return address). AR holds the effective address 135. This is shown in part (a) of the figure. The BSA instruction performs the following numerical operation:

## $M[135] \leftarrow 21, PC \leftarrow 135 + 1 = 136$

The result of this operation is shown in part (b) of the figure. The return address 21 is stored in memory location 135 and control continues with the subroutine program starting from address 136. The return to the original program (at address 21) is accomplished by means of an indirect BUN instruction placed at the end of the subroutine. When this instruction is executed, control goes to the indirect phase to read the effective address at location 135, where it finds the previously saved address 21. When the BUN instruction is executed, the effective address 21 is transferred to PC . The next instruction cycle finds PC with the value 21, so control continues to execute the

instruction at the return address. The BSA instruction performs the function usually referred to as a subroutine call. The indirect BUN instruction at the end of the subroutine performs the function referred to as a subroutine return. In most commercial computers, the return address associated with a subroutine is stored in either a processor

register or in a portion of memory called a stack. This is discussed in more detail in Sec. 8-7. It is not possible to perform the operation of the BSA instruction in one clock cycle when we use the bus system of the basic computer. To use the memory and the bus properly, the BSA instruction must be executed With a sequence of two microoperations:

$$D_5T_4: M[AR] \leftarrow PC, AR \leftarrow AR + 1$$

$$D_5T_5: PC \leftarrow AR, SC \leftarrow 0$$

Timing signal T4 initiates a memory write operation, places the content of PC onto the bus, and enables the INR input of AR. The memory write operation is completed and AR is incremented by the time the next clock transition occurs. The bus is used at T5 to transfer the content of AR to PC.

## **ISZ: Increment and Skip if Zero**

This instruction increments the word specified by the effective address, and if the incremented value is equal to 0, PC is incremented by 1. The programmer usually stores a negative number (in 2's complement) in the memory word. As this negative number is repeatedly incremented by one, it eventually reaches the value of zero. At that time PC is incremented by one in order to skip the next instruction in the program. Since it is not possible to increment a word inside the memory, it is necessary to read the word into DR, increment DR, and store the word back into memory. This is done with the following sequence of microoperations:

Figure 5-11 Flowchart for memory-reference instructions.

$M[AR] \leftarrow DR$ If (DR = 0)

SC ← 0

then  $(PC \leftarrow PC + 1)$

# **Input-Output and Interrupt**

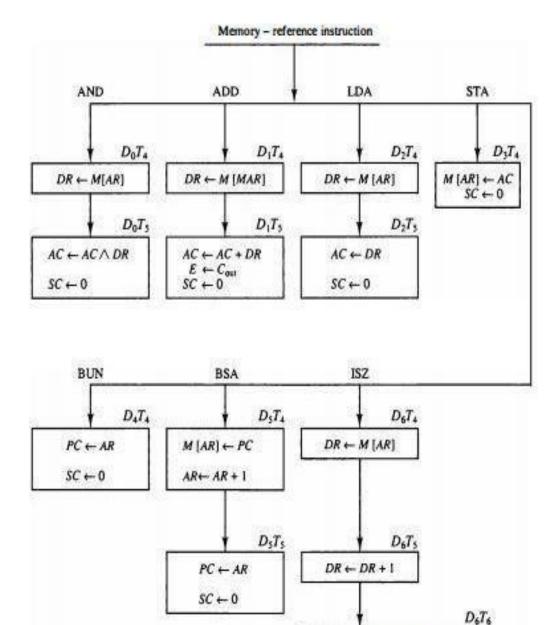

## Input-Output Configuration:

How input and output devices communicate, with each other using certain interfaces, flipflops and registers.

Printer , keyboard  $\rightarrow$  input-output terminals

Receiver interface, transmitter interface  $\rightarrow$  serial common interface

OUTR, INPR  $\rightarrow$  COMPUTER REGISTERS

FGO, FGI→ FLIPFLOPS

The INPR and OUTR are eight bits.

The 1bit Input flag FGI is a control flip-flop. The flag bit is set to 1 when new information is available in the input device and is cleared to 0 when the information is accepted by the computer. If flag set to 1 the computer checks the flag bit i.e information from AC to OUTR and FGO is cleared to 0.

Input output instruction have an operation code 1111

D<sub>7</sub>=1 and I=1

These instructions are executed with the clock transition T<sub>3</sub>

D<sub>7</sub>=1 I T<sub>3</sub>=P (common to all input-output instruction)

| TABLE 5-5 | Input-Output | Instructions |

|-----------|--------------|--------------|

|-----------|--------------|--------------|

| D7IT3 | = p (con     | mon to all input-output instructions)        |                      |

|-------|--------------|----------------------------------------------|----------------------|

| IR(i) | $= B_i$ [bit | in $IR(6-11)$ that specifies the instructi   | on]                  |

|       | p:           | <i>SC</i> ←0                                 | Clear SC             |

| INP   |              | $AC(0-7) \leftarrow INPR, FGI \leftarrow 0$  | Input character      |

| OUT   | pB10:        | $OUTR \leftarrow AC(0-7), FGO \leftarrow 0$  | Output character     |

| SKI   | $pB_9$ :     | If $(FGI = 1)$ then $(PC \leftarrow PC + 1)$ | Skip on input flag   |

| SKO   | $pB_8$ :     | If $(FGO = 1)$ then $(PC \leftarrow PC + 1)$ | Skip on output flag  |

| ION   | $pB_7$ :     | $IEN \leftarrow 1$                           | Interrupt enable on  |

| IOF   | $pB_6$ :     | $IEN \leftarrow 0$                           | Interrupt enable off |

## **Program Interrupt**

During an instruction cycle how an interrupt is handled.

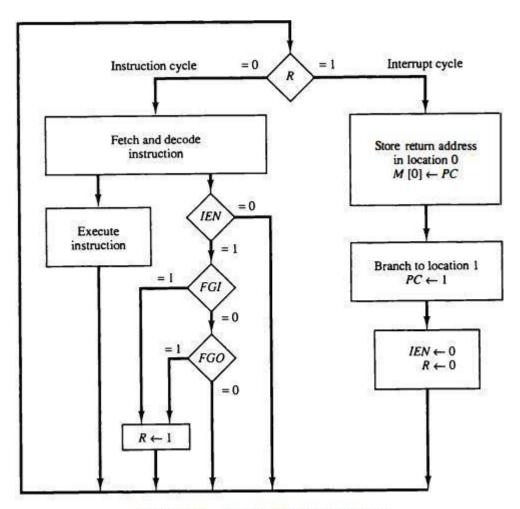

Figure 5-13 Flowchart for interrupt cycle.

IEN-Interrupt enable flipflop

R-Interrupt flipflop

FGO-1 bit output flag

FGI-1 bit input flag

- The value of R determines whether it enters the interrupt cycle or instruction cycle.

- If 0 the normal instruction cycle executed i.e fetch and decode instruction.

During execution phase there is another interrupt IEN-interrupt enable flipflop.

If IEN=0 means no interrupt and normal execution takes place.

If IEN=1 then it is checked for the input or output interrupt.

If FGO and FG1 both are 0 then no interrupts and normal execution takes place.

If FGI and FGO are one then R=1 has to be executed.

If R=1 then interrupt cycle is executed. first store return address then branch to location and then both value  $\text{IEN} \leftarrow 0, \text{R} \leftarrow 0$  set to zero

# **Central processing unit**

## **Introduction**

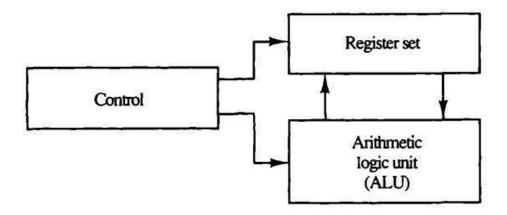

The part of the computer that performs the bulk of data-processing operations is called the central processing unit and is referred to as the CPU.

The CPU is made up of three major parts, as shown in Fig. 8-I

Figure 8-1 Major components of CPU.

- The register set stores intermediate data used during the execution of the instructions. The arithmetic logic unit (ALU) performs the required microoperations for executing the instructions.

- The control unit supervises the transfer of information among the registers and instructs the ALU as to which operation to perform.

## **General Register Organization**

- It is shown that memory locations are needed for storing pointers, counters, return addresses, temporary results, and partial products during multiplication.

- Having to refer to memory locations for such applications is time consuming because memory access is the most time-consuming operation in a computer.

- It is more convenient and more efficient to store these intermediate values in processor registers.

- When a large number of registers are included in the CPU, it is most efficient to connect them through a common bus system.

- The registers communicate with each other not only for direct data transfers, but also while performing various microoperations. Hence it is necessary to provide a common unit that can perform all the arithmetic, logic, and shift microoperations in the processor.

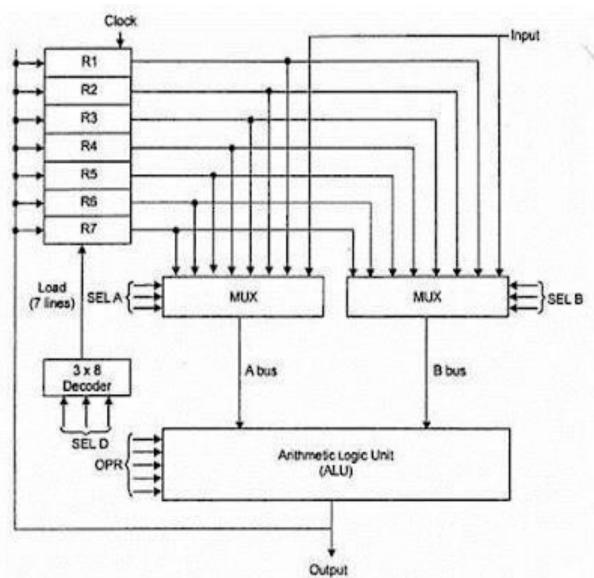

A bus organization for seven CPU registers is shown in Fig. 8-2. The output of each register is connected to two multiplexers (MUX) to form the two buses A and B.

- The selection lines in each multiplexer select one register or the input data for the particular bus.

- The A and B buses form the inputs to a common arithmetic logic unit (ALU).

- The operation selected in the ALU determines the arithmetic or logic microoperation that is to be performed.

- The result of the microoperation is available for output data and also goes into the inputs of all the registers.

- The register that receives the information from the output bus is selected by a decoder.

- The decoder activates one of the register load inputs, thus providing a transfer path between the data in the output bus and the inputs of the selected destination register.

- The control unit that operates the CPU bus system directs the information flow through the registers and ALU by selecting the various components in the system.

For example, to perform the operation the control must provide binary selection variables to the following selector inputs:

$$R1 \leftarrow R2 + R3$$

1. MUX A selector (SELA): to place the content of R2 into bus A.

2. MUX B selector (SELB): to place the content of R 3 into bus B.

3. ALU operation selector (OPR): to provide the arithmetic addition A+ B.

4. Decoder destination selector (SELD): to transfer the content of the output bus into R1.

tim

11

## **Control Word**

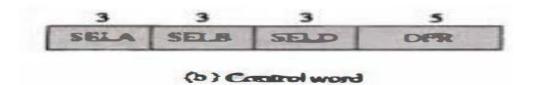

There are 14 binary selection inputs in the unit, and their combined value specifies a control word. The 14-bit control word is defined in Fig. 8-2(b).

It consists of four fields. Three fields contain three bits each, and one field has five bits. The three bits of SELA select a source register for the A input of the ALU. The three bits of SELB select a register for the B input of the ALU. The three bits of SELD select a destination register using the decoder and its seven load outputs. The five bits of OPR select one of the operations in the ALU. The 14-bit control word when applied to the selection inputs specify a particular microoperation.

| TABLE 8-1      | Encoding of | Register Se | election Fi |

|----------------|-------------|-------------|-------------|

| Binary<br>Code |             |             | SELD        |

| 000            | Input       | Input       | None        |

| 001            | R1          | R1          | <b>R1</b>   |

| 010            | R2          | <b>R2</b>   | <b>R2</b>   |

| 011            | R3          | R3          | R3          |

| 100            | R4          | R4          | R4          |

| 101            | <b>R5</b>   | <b>R5</b>   | <b>R5</b>   |

| 110            | R6          | R6          | R6          |

| 111            | <b>R7</b>   | <b>R7</b>   | <b>R7</b>   |

The encoding of the register selections is specified in Table 8-1.

- 11

The encoding of the ALU operations for the CPU is taken from Sec. 4-7 and is specified in Table 8-2. The OPR field has five bits and each operation is designated with a symbolic name.

| OPR    |                |        |

|--------|----------------|--------|

| Select | Operation      | Symbol |

| 00000  | Transfer A     | TSFA   |

| 00001  | Increment A    | INCA   |

| 00010  | Add $A + B$    | ADD    |

| 00101  | Subtract A – B | SUB    |

| 00110  | Decrement A    | DECA   |

| 01000  | AND A and B    | AND    |

| 01010  | OR A and B     | OR     |

| 01100  | XOR A and B    | XOR    |

| 01110  | Complement A   | COMA   |

| 10000  | Shift right A  | SHRA   |

| 11000  | Shift left A   | SHLA   |

TABLE 8-2 Encoding of ALU Operations

## **Examples of Microoperations**

A control word of 14 bits is needed to specify a micro operation in the CPU. The control word for a given microoperation can be derived from the selection variables.

For example, the subtract micro operation given by the statement R1 < -R2 - R3 specifies R2 for the A input of the ALU, R3 for the B input of the ALU, R1 for the destination register, and an ALU operation to subtract A - B.

Thus the control word is specified by the four fields and the corresponding binary value for each field is obtained from the encoding listed in Tables 8-1 and 8-2.

The binary control word for the subtract micro operation is 010 011 001 00101 and is obtained as follows:

| Field:        | SELA | SELB | SELD | OPR   |

|---------------|------|------|------|-------|

| Symbol:       | R2   | R3   | R1   | SUB   |

| Control word: | 010  | 011  | 001  | 00101 |

### **Stack Organization**

A useful feature that is included in the CPU of most computers is a stack or last-in, first-out (LIFO) list. A stack is a storage device that stores information in such a manner that the item stored last is the first item retrieved.

The stack in digital computers is essentially a memory unit with an address register that can count only (after an initial value is loaded into it).

**The register that holds** the address for the stack is called a stack pointer (SP) because its value always points at the top item in the stack.

The two operations of a stack are the insertion and deletion of items. However, nothing is pushed or popped in a computer stack. These operations are simulated by incrementing or decrementing the stack pointer register.

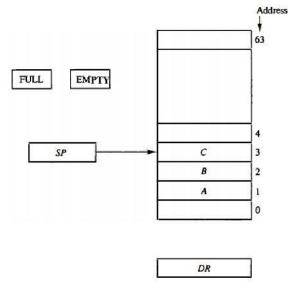

**Register Stack** A stack can be placed in a portion of a large memory or it can be organized as a collection of a finite number of memory words or registers. Figure 3 shows the organization of a 64-word register stack. The stack pointer register SP contains a binary number whose value is equal to the address of the word that is currently on top of the stack. Three items are placed in the stack: A, B, and C, in that order. Item C is on top of the stack so that the content of SP is now 3.

Figure 8-3 Block diagram of a 64-word stack.

- To remove the top item, the stack is popped by reading the memory word at address 3 and decrementing the content of SP

- Item B is now on top of the stack since SP holds address 2. To insert a new item, the stack is pushed by incrementing SP and writing a word in the next-higher

location in the stack. Note that item C has been read out but not physically removed.

- This does not matter because when the stack is pushed, a new item is written in its place. In a 64-word stack, the stack pointer contains 6 bits because  $2^6 = 64$ .

- Since SP has only six bits, it cannot exceed a number greater than 63 (111111 in binary). When 63 is incremented by 1, the result of since 111111 + 1 = 1000000 in binary, but SP can accommodate only the six least significant bits.

- Similarly, when 000000 is decremented by 1, the result is 111111. The one-bit register FULL is set to 1 when the stack is full, and the one-bit register EMPTY is set to 1 when the stack is empty of items. DR is the data register that holds the binary data to be written into or read out of the stack.

- **Initially**, SP is cleared to 0, EMPTY is set to 1, and FULL is cleared to 0, so that SP points to the word at address 0 and the stack is marked empty and not full. If the stack is not full (if FULL = 0), a new item is inserted with a push operation.

- **The push operation** is implemented with the following sequence of microoperations;

- SP  $\leftarrow$  SP + 1 Increment stack pointer

- $M[SP] \leftarrow DR$  Write item on top of the stack

- If (SP = 0) then  $(FULL \leftarrow 1)$  Check if stack is full

- EMPTY  $\leftarrow 0$  Mark the stack not empty

- The stack pointer is incremented so that it points to the address of the next-higher word. A memory write operation inserts the word from DR into the top of the stack. Note that SP holds the address of the top of the stack and that M[SP] denotes the memory word specified by the address presently available in SP.

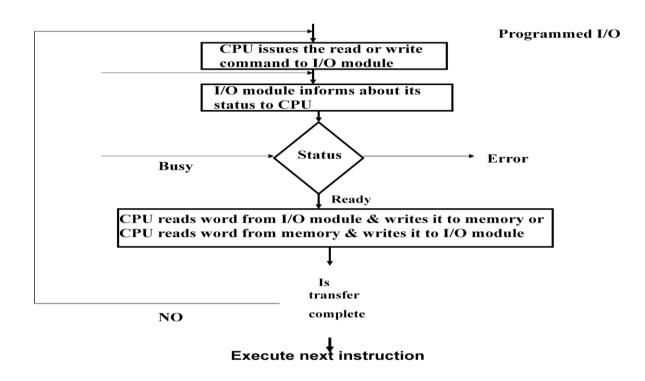

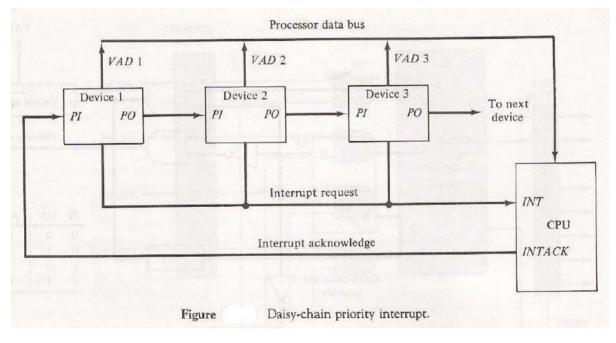

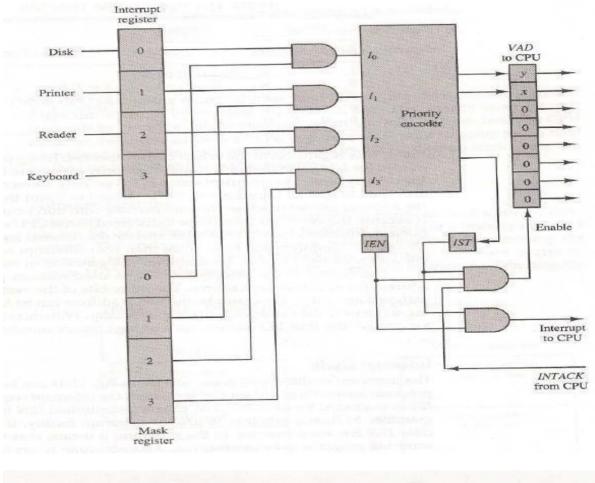

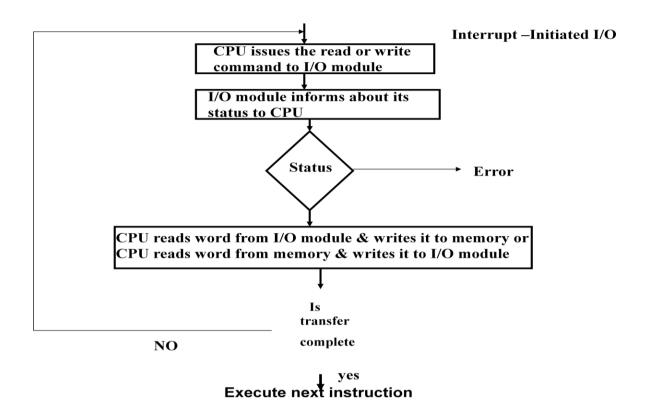

- The first item stored in the stack is at address L The last item is stored at address 0.